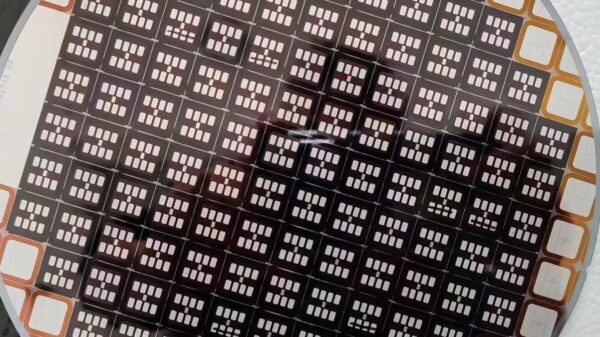

In a significant move to bolster energy efficiency in data centres, Marvell Technology is set to introduce high-speed silicon interconnects created using Taiwan Semiconductor Manufacturing Company’s (TSMC) revolutionary 3nm process technology. According to Mark Kuemerle, Marvell’s Vice President of Technology, this innovation would lead to chiplet connections that drastically reduce power consumption.

The cutting-edge die-to-die (D2D) interconnect designed by Marvell enables data transmission speeds of up to 240T bits per second (bps), a 45% enhancement over the existing interconnects used in multi-chip packages. The company envisages employing this new building block to design Intellectual Property (IP) that optimises bandwidth, performance, and energy efficiency in data centres, as well as in the burgeoning self-driving car industry.

Through this initiative, Marvell aims to facilitate multi-chip construction without resorting to expensive silicon interposers for interconnects. The implications extend beyond data centres, with a growing trend towards multi-chip integration in automotive chips in response to the accelerating drive to optimise power performance and cost.

Marvell’s adoption of TSMC’s groundbreaking 3nm node, a key aspect of its development strategy, underlines the reliability of this leading-edge technology. Notably, Marvell ranks among TSMC’s top 10 clients, as per the UK-based equity research firm Arete Research.

The industry’s pioneering 3nm node components, including 112G XSR (eXtra Short Range) SerDes, Long-Reach (LR) SerDes, PCIe Gen 6/CXL 3.0 SerDes, and 240Tbps parallel D2D interconnects, are incorporated by Marvell, making it the industry’s first to offer 112G SerDes and data infrastructure products on TSMC’s 5nm process.

Marvell projects that its novel IP will initially serve customers developing chips for data centres. Alan Weckel, an analyst at 650 Group, commented, “Marvell’s successful manufacture of SerDes and interconnects for the 3nm process marks a significant advancement in assisting cloud service providers to keep pace with the soaring speed and traffic demands.”

With the new technology, Marvell anticipates reducing data centre power consumption by as much as 20 percent. Kuemerle notes that bringing these components closer on a single package could enhance power efficiency by a factor of 10. This is significant as the interconnect power often accounts for just over a third of the total device power consumption.

The novel interconnect will play a crucial role in reducing the carbon footprint of data centres, a significant issue considering that training AI’s large language model has a carbon footprint of approximately 300,000 kg, equivalent to 125 round-trip flights between New York and Beijing.

While the focus is on power consumption, Marvell is also addressing thermal problems associated with the technology. Kuemerle states that the firm is diligently exploring innovative thermal solutions.

The automotive industry is another potential beneficiary of the new technology. Despite the inherent challenges of a multi-chip environment, Kuemerle sees tremendous opportunity in the realm of automotive ASICs and advanced driver assistance systems (ADAS) with machine learning. The company also recognises the potential of new PCIe-related activities for automotive applications.

As the automotive sector grapples with a persistent semiconductor shortage, solutions like Marvell’s are poised to make a significant impact. Marvell anticipates the eventual availability of TSMC’s 3nm technology to other foundries, setting the stage for an industry-wide standardisation of the interconnect and offering fabs a broader range of options for pre-made components.